Projekt 5: Multiplexer, avkodare, kodare och Växelreglage

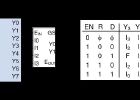

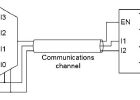

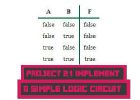

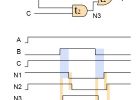

I detta projekt kommer du designa en multiplexer, en dekoder, en kodare och en shifter med Verilog HDL. Istället för att bygga banan med hjälp av logiska operatorer, lär du dig att beskriva en krets behaviorally enligt den funktionalitet du vill gå r...