Digitalt oscilloskop med Digilent Zybo styrelsen (1 / 6 steg)

Steg 1: Analog Front End

Xilinx Zynq IC har "XADC" Analog till Digital omvandlare. XADC proverna med ett maximum av 1MSPS (megasample per sekund), mata en 12 bitars värde. Denna ADC har en indataområdet för 0-1V.

XADC kan provtagning flera ingående kanaler, men i Zynq styrelsen bara flera specifika extraingångar kan faktiskt nås av användaren. I min oscilloskop använde jag AUX14 ADC ingång tillgänglig på XADC PMOD av Zybo.

Eftersom ett oscilloskop indataområdet för 0-1V inte är särskilt användbar, måste analoga kretsar läggas framför ADC indata för att skala och skifta inspänningen, se blockdiagram för detta steg.

Denna blockdiagram genomfördes med hjälp av de kretsar som visas i LTSPICE schematiska/simulering (Schematisk fil bifogas för simulering). Som önskat, vinsten är 1/20 = 0,05 tills anti-aliasing filter orsakar det att släppa ut cirka 400kHz (nyquist frekvens = 500kHz för 1MSPS ADC).

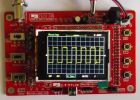

Jag genomfört denna design på en skärbräda (hade inte tid att design en PCB) med via hål komponenter. De komponenter som används för att implementera denna design visas i den andra LTSPICE schematiskt (inte simulatable, bara används för att utforma krets för beställning av delar), samt faktiska byggda banan också. De 3.3V och GND hade sitt ursprung från XADC PMOD kontakten.