LEDDE fladdrande fackla (1 / 6 steg)

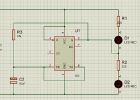

Steg 1: Den Controller Design schematiskt

Registeransvarige är baserad på en ATMega324P i en 44 pin TQFP paketet. Schematiskt drogs Geda's gschem verktyg. Titta på den schematiska som fästas både PNG och gEDA/gschem formatet.

En RGB gemensam anod LED är ansluten vid CONN2, detta är en 3W modell från Everlight som jag hittade överskott. Varje segment av detta LED kan hantera 3W så det var nödvändigt att köra katoder med drivatransistorerna Q4, A5 och Q6. Denna särskilda AVR valdes eftersom det lyfter fram 3 PWM kanaler av inre timers till stiften. Detta gör att oberoende ljusstyrka av färgkanalerna R, G och B.

Både ett ISP-huvud (J9) och JTAG (J12) kommas med ut för programmering och felsökning. Bara rubriken ISP krävs, men jag ville experimentera med JTAG också.

CPU (U1) är klockat av en 20MHz kristall, X1.

Styrelsen drivs av 5V, med möjlighet till en 12V genomslag vid ett senare tillfälle.

Andra funktioner som inte behövs i detta syfte inkluderar U2 ULN2803A hög effekt buffert för att köra andra laster från Port A av CPU, samt 3 kanaler som kan köra reläer på 12 V på J2, J3 och J4. De andra timer utgångar som inte används är fast ut på J8 och J11 så småningom styra servomotorer. Allmänna ändamål IO (GPIO) tillhandahålls på J5, J7 och J10.