Att komma igång med Xilinx Vivado w / Digilent Nexys 4 FPGA 1 - bygga flera ingångar och logik utfärda utegångsförbud

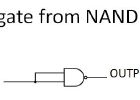

Jag gör detta instructable eftersom det ser ut som det inte är enkelt att komma igång handledning för att lära människor att använda den senaste Xilinx Vivado CAD-verktyget. Så, jag vill använda den enkla flera ingångar gate design att gå igenom Xilinx Vivado CAD. Jag kommer att använda Verilog hårdvara Design språk för att skapa den logik designen. Designen kommer att genomföras sedan i Digilent Nexys 4 FPGA (Field Programmable Gate Array) utveckling styrelsen.

Digital / Logic design är en grundläggande men viktiga kunskap. Det är utformningen av kretsar och system som utgör basen för all elektronik. FPGAs är programmerbara halvledarkomponenter baserade runt en matris av konfigurerbara logik block (CLB) ansluten via programmerbara interconnects. Om du vill veta mer om FPGA, kan du gå till Xilinx eller Nationella instrument webbplats.

Verilog är basedon programspråket C och är den vanligaste i konstruktion och verifiering av digitala kretsar på register-överföring nivå av abstraktion. Du kan ta reda på detaljerna i Digilent Intro till Verilog projekt