BitRunner FPGA spelet (3 / 4 steg)

Steg 3: Programmering av FPGA

Använda Xilinix Design Suite kan du sätta ihop filerna in i ett fungerande system av moduler. Du kan följa stegen här till få den. För ett tekniskt geni som själv montering detta bör ingen big deal, men om du behöver ytterligare förklaringar på modulerna, det finns kommentarer inom de uppladdade vhd-filerna. Du kan ignorera anteckningarna under varje del i det här steget om du inte behöver en förklaring på hur man genomföra modulen eftersom du är en sådan teknisk geni.

En sak till innan vi kommer in i detta

För en tydligare eller mer i djup svart låda diagram.

-Hämta och syntetisera våra vhd moduler

-Expandera alternativet synthesize och dubbelklicka på "Visa RTL Schematisk"

-Dubbelklicka på svarta lådan diagram att expandera den

Del 1. Skapa ett hinder skiftregister. Du behöver en klocka avdelare göra SKIFT register hinder köras i begriplig hastigheter.

-Inledningsvis ge 8-bitars skiftregister en '1' att börja hinder.

-på varje rising_edge(clk) efter det

---Flytta bitar genom att skicka den (6 CEN. 0) till den (7 CEN. 1) på "nästa" signalen (lfsr_next) som vi kallade det.

---Ange den 1: a lite på "nästa" signal till biten av den aktuella register "xor" en annan bit av det aktuella registret

---Du kan välja någon två bitar till xor, detta helt enkelt kommer att resultera i en pseudoslumptalsgenerering ordning.

---Det har några slumpmässiga egenskaper, men mönstret upprepas.

Anmärkning 1: SSEG dekoder och Clk_div ges till oss av våra lärare. Dessa moduler har skapats av Professor Bryan Mealy på Cal Poly Slo. Sseg avkodaren tar en 8 bitars tal och visar att många i decimal på sju segment display. Clk_div är en klocka avdelare som sträcker ut clk perioden. Bara kopiera, klistra in det i. Varning: Sseg dekodern kan ge varningar om hur disken är oanvända. Detta beror på att räknaren når aldrig att höga av flera att kräva vissa bitar. Således vhdl optimerar dessa bitar och spottar en varning ut.

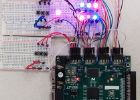

Kontrollera att dessa moduler arbete genom att ladda upp ditt program och titta på lysdioderna lyser upp. Om gjort korrekt, bör din hjärna tänka att ljusmönstret som avges är på väg som hinder till vänster. Vid detta är inte sant, kolla inställningen bakbord, moduler och din egen hjärna.

Del 2. Skapa den poäng avkodaren. Modulen ger en poäng baserad på tiden, i huvudsak är det en räknare. Inget spel är komplett utan en kall, opartiskt sätt särskilja hur dålig du är i jämförelse med andra. Var noga med att skapa en modul liknande sseg_dec.vhd så att du och dina döma kamrater kan visa poäng på sju segment display med lätthet.

-På stigande kanten av clk efter det genom clk_div, öka poäng

Testa om detta fungerar genom att simulera det. Se till du nummer steget korrekt. Du kan ytterligare testa genom att skicka din poäng dekoder produktion till sseg_dec att bestämma det fungerar visuellt. Poängen ska öka med ett för varje stigande klocka kant.

Anmärkning 2: När simulera poängen avkodaren, fönstret av simuleringen är inom några nanosekunder, så minska din klocka faktor 1 för korrekt resultat. Annars kommer inget tycks hända.

Del 3. Kombinera SKIFT Register och poängen avkodaren med en huvudsaklig modul. Vara säker på att ha klocka avdelare som klockan för både skiftregister och poäng. Slutresultatet bör ha en poäng som ökar stegvis på varje SKIFT av hinder.

Del 4. Skapa en modul för knappen dekoder. Det tar i indata från en knapp och avgör om spelaren är i dodge tillstånd eller inte. Detta krävs för att hindra spelare från att hålla nere knappen dodge och ducka alla mötande hinder.

-Denna modul kan representeras med en ändlig tillståndsdator, representerade i den bifogade ändliga tillståndsdiagram

-Defaults vänta staten

-Om du inte trycker på knappen stannar staten i vänta-läge

-Om de gör det, då det går för att undvika läge och utgångar dodge för en viss tid

---Detta bestäms av en clk som räknar till ett visst antal på stigande kanten (upp till dig)

-Efter avslutad dodge läge, det automatiskt går till let_go staten och gå inte tillbaka till vänta staten tills spelaren släpper knappen.

Del 5. Skapa en modul för att kontrollera om spelaren drabbas av blocket och att spelet är över.

-Spelet är över om hindret i slutet på och spelaren inte är i dodge läge.

-Om spelet är slut kan du välja att återställa skiftregister och score_decoder, vilket vi gjorde

--- Eller du kan vänta på en förbrukaren insatsen starta om spelet

Detta testades med en simulering fil. Vi ange indata till olika kombinationer och visuellt bekräftade riktigheten.

Del 6. Sätta detta ihop i du huvudsakliga modul och köra spelet i filen begränsningar.

-Mappningarna mest stift finns i styrelsen.

-För de LED sladdar som ska anslutas, måste du leta upp det på webbplatsen för styrelsen. Om du använder en NEXYS 3 ombord, kan du använda våra begränsningar/implementeringsfilen som kommenterar vad pins är på bordet.

-Testa detta med simulering också. Det är lätt att se vad som händer med en simulerad fil eftersom du kan titta på resultaten av de olika modulerna också.

Observera 3: Du kommer att få samma varningar som not 1 med några andra moduler av samma anledning.

Del 7. Valfria. (Obligatorisk om alla delar innan detta var en barnlek för dig) Ändra allt med en klocka avdelare och knappen dekodern i räkningen (gör inte detta för sseg dekoder). Detta sätt som poäng ökar du kan passera olika antal och snabba upp spelet för att öka svårigheten.

Anmärkning 4: Om du gör det kan du få några extra varningar, påstå att du har skapat en spärr. Simuleringarna gjordes även innan detta, så du måste lägga till de tilldelningarna om du vill simulera efter tillsats.

Anmärkning 5: Du får en varning om att vissa saker köps av en kombinatorisk pin. Detta är bra, det kommer inte att påverka spelet.

Del 8. Ladda upp filen bit till din FPGA. Eftersom trots allt detta arbete, din FPGA gör fortfarande ingenting. Att göra detta ladda ner och installera ett program som heter Adept.

Du kan få den här http://www.digilentinc.com/Products/Detail.cfm?Nav...

När du har installerat den ansluta micro USB-sladden till FPGA och markera filen bit. Tryck sedan på program. Om du har nått denna del utan att hoppa över några åtgärder borde då en liten spel vi kallar vårt projekt sitta framför dig.