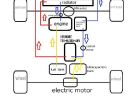

Cordic algoritm använder VHDL (2 / 3 steg)

Steg 2: VHDL-kod för konstruktion och provbänken

---Riktlinjer---

Simulera cordic_v4.vhd - Design

(1) input är vinkel i 32 bitar + teckenbiten; den kan behandla alla vinklar från 0 till +/-360 graders med input precision av 0.000000000233 grad. När att ge input -> MSB är teckenbiten och resten 32 bitar representerar magnituden.

(2) produktionen av designen är dess sinus och cos värde i 16 bitar + tecken bit .ie; med precision 0.00001526. Observera att utdata visas i 2: s förgyller form om respektive sinus eller cos värdet är negativt.

Simulera testb.vhd - Test bänk för Design

(1) efter två steg av simulering dra återställa till "1" och "köra alla".

(2) i simulering som fönstret radix av synd och cos signaler som decimal och format > Analog (automatisk).

(3) zooma ut för att se vågformen ordentligt.