Digitala filter Zybo ombord (3 / 14 steg)

Steg 3: Lägga till anpassade Verilog moduler

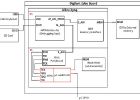

Vi kommer att lägga till en anpassad VHDL moduler. Modulen som ska läggas till blir den I2S controller som har genererats med hjälp av modulen axi_i2s_adi_v1_0 pre. Den här modulen innehåller filer i2s styrenheten som användes för att generera bclk och lrclk. Filerna för denna IP finns i huvudmappen. I2S kommunikationsprotokoll kräver en bclk vara långsammare än mclk(master clk). Den basen klockan helst ska vara mclk/4 och mclk bör 12.288 MHz. Vi vill prova våra ljud på 48 MHz så dessa inställningar tas ifrån den ljud-codec Specifikationsblad. Lrclk signalen måste vara bclk/64 eftersom för vänster kanal kommer vi prova 32 bitar och sedan för den högra kanalen kommer vi prova 32 bitar. I princip så snart data upptäcks genereras klockorna. Som vi provsmakar hela tiden genereras klockan kontinuerligt. Alla codec information kan nås på http://www.analog.com/en/products/audio-video/audi... .

Inställningarna för detta I2S för styrenheten kommer att ges i senare steg.