Digitala filter Zybo ombord (4 / 14 steg)

Steg 4: Skapa The Custom VHDL moduler

Nu måste du skapa VHDL-kod för att bygga ett 64-bitars ljud prov med den inkommande datan från codec. 64 bitar står för 32 bitar från vänster kanal och 32 bitar från den högra kanalen. Detta ljud prov blir sedan indelade i dess vänstra och högra komponenter och filtreras innan han återvände tillbaka till dess full 64 bit sampels längd. I vårt genomförande är vårt verkliga ljud endast 12 bitar lång. Detta kräver att lägga till nollor till LSBs av höger och vänster ljud proven separat efter filtrering och innan data är åter serialiserade.

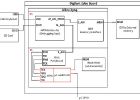

Modulen skapad tar i seriell data, I2S LRCLK, I2S BCLK, en 50MHz klocka (CLK), en återställning och en kontroll stift att ändra effekterna. Blocket diagrammet nedan Detaljer SerialEffects blocket inre funktionalitet.

Funktionerna i varje block samt deras in- och utgångar finns beskriven i siffrorna ovan.

LRCLK: Används av personliga RX och personliga TX för att skilja mellan vänster och höger kanaler.

BCLK: Används av personliga RX och personliga TX som bit klockan att läsa eller skriva seriella CLK: 50MHz används av distorsion filter för att behandla uppgifterna.

Koden för dessa moduler ges nedan. Använd den bifogade serialIP zip arkivera över de som föreskrivs i den ursprungliga mappen serialIP IP-blocket.