Projektet 2.1: Genomföra en enkel logik krets (15 / 19 steg)

Steg 15: Genomföra krets 1 i Verilog HDL

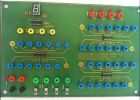

Bygga upp och genomföra logik ekvationen för krets 1 enligt tabellen sanningen. Vi kommer att bygga logik ekvationen i SOP för demonstration. I krets 1, vi har två rader (andra raden och tredje raden) som visar "1" i utdata. Så behöver vi en eller-grind med två ingångar som genererar utdata, och två 2-input och grindar som ger indata för eller-grind. I den andra raden, ingång SW0 visar "1" och input SW1 visar en "0". Så SW0 är ansluten till ingången på den första och-grinden och SW1 är inverterad innan du ansluter till den andra ingången och grinden, som visas i den första produkt termen i ekvationen. Den tredje raden, indata-SW0 visar en "0" och input SW1 visar "1". Så SW0 är inverterad innan du ansluter till ingången av den andra och-grinden och SW1 är ansluten direkt till den andra ingången och grinden, som visas i den andra produkt termen i ekvationen. Produktionen LD0 är summan av dessa två produktvillkor.

Verilog HDL genomförs denna krets som ovan.