Lärande sekventiella logik Design för en Digital klocka (10 / 14 steg)

Steg 10: 1 - 12 stick i stäv med T - FF

Detta är den tuffaste counter för partiet, så förklaringen kommer att bli en lite sträckt.

Vi kan inte använda IC 7493 för detta counter också. Vi inte kan använda det för en 1-12 räknare eftersom utfärda utegångsförbud för NAND utgången ansluts till alla Clear bara inte FÖRINSTÄLLNINGEN. I själva verket att bäst jag vet finns det inga andra IC räknare som har förinställda funktioner.

Så måste vi bygga den här räknaren från grundläggande flip-flops. Det är där kunskapen om sekventiella logik vi diskuterade från steg 3 till steg 8 kommer händig.

Vi kunde ha en enkel 1-12 counter från 4 flip flops och använt en binär till BCD-omvandlare och använda det för bildskärmar. Man måste komma ihåg att displayerna kan endast Visa siffrorna 0 - 9. Så direkt tillämpa 10, 11 & 12 binära värden kommer att ge en oönskad effekt. Så måste vi använda en binär till BCD-omvandlare eller IC 74185. Som var planen från början om du refererar blockdiagram visades tidigare.

Det råkar vara så att IC 74185 inte är tillgänglig på marknaden (om du får en du har tur sedan använda schematiskt i den första skannade filen), så vi inte kan bara göra en 1-12 räknare. Vi måste hitta ett annat sätt runt den.

Sedan jag var helvetet böjd på att få en 1-12 räknare för mina timmar (det är kanske därför de flesta andra klockor har 0 - 23 räknare, är det lätt), jag hittade en lösning. Tricket var att använda 4 T flip flops tillsammans med 1 D Flip Flop. 4 T flips flops är ansluten till den första visningen (höger sida en) och en D flip flop är ansluten till andra (vänster sida).

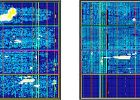

4 T Flip Flop är ansluten till att arbeta som en 0 - 9 counter som i steg 7. Nummer 10 (1010) används som Återställ trigger, så Q3 & Q1 är anslutna till en NAND utfärda utegångsförbud för vars produktion avmarkerar alla T flip flops och förinställning D flip flop till 1. Så den totala produktionen nu är 1 0. Då T flip flops räkna igen från 0 till 1 och sedan 2 motsvarande totala utgångar skulle vara 10, 11 & 12. Nu 3 (0011) är krävs reset utlösa men Q av D vänd floppen används också. Q d flip flop och Q1 & Q0 4 bitar T flip flop counter är ansluten till ett 3 input NAND gate. Resultatet av den 3 input NAND porten ges till Clear alla flip flops utom Q0. T vänd floppen motsvarar Q0 är presetted till 1. Så får vi 0 1 som den totala produktionen. Således får vi räknaren 1-12.

Detta är teoretiskt, praktiskt när jag hade utgångar från två NAND-grindar ansluten till Clear av flip flop parallellt, så händer det att funktionen clearing är alltför skriftlig och vi får en gratis strider. Detta beror på att när en NAND utgång är 0 (Låt oss säga dess 0 eftersom räknaren T flip flop läser 1010 och rensa), andra NAND utgången är 1 (när produktionen är 9 kom ihåg D vänd floppen Q är 0, så att NAND utdata är 1). Så, 0 från första NAND som bör ha rensat räknaren till 0 inte klara något på grund av de 1 ansluten i parallellen. För att övervinna detta två NAND är utgångar anslutna till en AND-gate vars produktion är med tanke på Clear och förinställning. Så när en NAND gate är 1 och den andra 0, produktionen är 0 som utlöser förändringen men i de flesta fall blir båda utgångarna 1 och och produktionen är också 1. (De två NAND-utgångarna kan aldrig både vara 0 för 10 inte är lika med 13)

Det är verkligen svårt att skriva med ord, det tog mig 7 timmar för att korrigera fel efter fel för slutresultatet. Jag hoppas du finner de logiska diagram i andra skannade filen användbart.

Komponenter:

IC 7476:2 nr.

IC 7474: 1 nr.

IC 7410: 1 nr.

IC 7408: 1 nr.

IC 7447:2 nr.

Gemensam anod 7 segment display: 2 nr.

IC 555: 1 nr.

Kondensatorer: 1000 uF och 0,01 uF (1)

Motstånd: 470 ohm (1), 500 ohm (1) och 330 ohm (13)

Komponenter skulle vara två 7476 IC som 4 T flip flops erhålls. 1 D flip flop 7474 (om du märker, D vänd floppen utgång är antingen 0 eller 1 alternativt, så ja du kan alternativt använda en annan T flip flop också). Du behöver också en 3 input NAND gate IC 7410 och en AND-gate IC 7408.

Konstruktion:

Först den 4 lite T flip flop counter som sett i steg 7.

Se om det fungerar, använda en 3 input NAND grind med 1 ingång ansluten till Vcc och de andra två är Q3 och Q1 av T flip flop counter.

Ta att NAND utgång till ingången på en AND-gate (terminal 1) och även förinställningen i D flip flop. Kom ihåg att varje och IC 7408 har 4 och portarna.

Således att när T flip flop counter går till 1010, D flip flop växla till 1 medan 4 T flip flops klart för 0.

Q D Flip är flop ansluten till ingången på en annan NAND gate. Q1 & Q0 är också anslutna till samma NAND grinden. Sin produktion till AND-gate (terminal 2) och också klart D flip flop.

Produktionen av AND-gate (terminal 3) är ansluten till klartext av Q3 & Q1.

Lämna den tydlig och förinställda för Q2 & Q0 orörda, får du fortfarande krävs utdata.

Detta kommer att förklara varför. Den första röjningen uppstår när T flip flop räkningen är 1010 (10), så vi får om Q3 & Q1 har rensats, 0000 vilket är vad vi vill. Den andra clearingen uppstår när räknaren T flip flop är 0011 (ofcouse D's Q är 1 också men det är irrelevant), så igen om vi klara bara Q3 & Q1, produktionen är 0001, som är igen vad vi vill! Så, kan du lämna Q2 & Q0 orörd.

Detta är en av de få gånger när du designar kretsar, som du hittar kretsen förenklar själv!

Många gånger när vi utformar en krets, vi kanske inte får de komponenter som krävs eller de kan vara alltför kostsamt som IC 74185. I sådana fall kan du alltid skapa en sinnrik konstruktion som fungerar med vad som finns men fortfarande ger de resultat du vill. Detta är ett exempel på detta.