Projekt 5: Multiplexer, avkodare, kodare och Växelreglage (9 / 10 steg)

Steg 9: Designa en Shifter

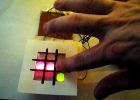

I det här avsnittet ska vi utforma en 4-input Shifter. Fyra ombord växlar används som data ingångar. Tre andra bilden växlar fungerar som styrsignaler F, R och D. En tryckknapp kommer att användas som signal på Aktivera. Fyra lysdioder visar utdata från Växelreglage.

Skapa ett projekt i Xilinx Vivado inriktning FPGA styrelsen du använder, som i tidigare projekt.

Skapa en Verilog modul kallas "shifter" med ingångar I, sv, D, R, F och utgångar Y enligt följande:

() 1 modul decoder_3_8

2 ingång [3:0] I,

3 ingång D,

4 input R,

5 ingång F,

6 ingång En,

7 utgång [3:0] Y

8).

Liknar föregående steg, vi kommer att använda om uttalande igen för att genomföra Växelreglage.

1 reg [3:0] Y;

2

3 alltid @ (I, Ein)

4 börja

5 if (sv == 0)

6 Y = I.

7 annat

8 om (R == 0)

9 Y = (D == 0)? {I [2:0], F}: {F, JAG [3:1]};

10 annars

11 Y = (D == 0)? {Jag [2:0], jag [3]}: {jag [0], jag [3:1]};

12 avsluta

I föregående kod, {A, B} används för att sammanfoga två grupper av signaler till en buss. Till exempel Y = {i [2:0], F} betyder Y [3:1] = I [2:0] och Y [0] = F.

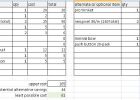

Skapa en XDC fil och karta:

-I [3:0] till SW3, SW2, SW1, SW0

-R att SW7, D till SW6, F till SW5

-En till Btn0

-Y [3:0] till ledde 3-0