Projekt 5: Multiplexer, avkodare, kodare och Växelreglage (2 / 10 steg)

Steg 2: Design en Multiplexer

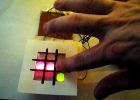

Detta projekt startar med att designa en 4-1 2-bitars buss multiplexer. Åtta ombord bilden växlar används för att tillhandahålla data ingångar, två tryck-knappar kommer att användas som Välj signaler och lysdioder 0 och 1 används för att visa utdata från multiplexorn. Istället för att genomföra en multiplexer med hjälp av logiska operatorer, vi kommer att beskriva kretsen behaviorally med en alltid block och en if-uttryck eller ett case-uttryck.

Presenterar vi tre olika sätt att koda multiplexorn behaviorally här. Dock behöver du bara en i din kod. Du uppmuntras att prova alla tre olika sätt för att förstå och uppleva skillnaden i Verilog syntax.

Skapa ett projekt i Xilinx Vivado inriktning FPGA styrelsen du använder, som ni har gjort i tidigare labs.

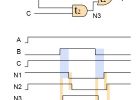

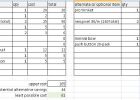

Skapa en Verilog modul som kallas mux_4_1 med ingångar I0, I1, I2, I3, Sel och utgång Y enligt följande:

() 1 modul mux_4_1

2 ingång [1:0] I0,

3 ingång [1:0] I1,

4 ingång [1:0] I2,

5 mata in [1:0] I3,

6 ingång [1:0] Sel,

7 utgång [1:0] Y

8).