Projekt 5: Multiplexer, avkodare, kodare och Växelreglage (5 / 10 steg)

Steg 5: Designa en binär avkodare

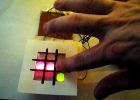

I detta avsnitt kommer vi att utforma en 3:8 binära avkodare. Switchar

0 till 2 används som insatsvaror för 3:8 dekoder och 8 ombord lysdioder används för att ange utdata från dekodern.

Skapa ett projekt i Xilinx ISE inriktning FPGA styrelsen du använder, som i de tidigare projekten.

Skapa en Verilog modulen kallas decoder_3_8 med ingång för jag och utgång Y enligt följande:

() 1 modul decoder_3_8

2 ingång [2:0] I,

3 utgång [7:0] Y

4).

Det mest effektiva sättet att beskriva funktionen hos en avkodare är att använda ett case-uttryck i en alltid blockera.

1 reg [7:0] Y;

2

3 alltid @ (I)

4 börja

5 fall (I)

6 3' d0:

7 Y = 8' d1;

8 3' d1:

9 Y = 8' d2;

10 3' d2:

11 Y = 8' d4;

12 3' d3:

13 Y = 8' d8;

14 3' d4:

15 Y = 8' d16;

16 3' d5:

17 Y = 8' d32;

18 3' d6:

19 Y = 8' d64;

20 3' d7:

21 Y = 8' d128;

22 standard:

23 Y = 8' d0;

24 endcase

25 slutet

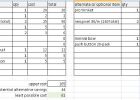

Skapa en XDC fil och karta:

-I [2:0] till SW2, SW1, SW0

-Y [7:0] till LED 7-0